科技日报记者 张盖伦

光刻技术是推动集成电路芯片制程工艺持续微缩的核心驱动力之一。近日,北京大学化学与分子工程学院彭海琳教授团队及合作者通过冷冻电子断层扫描(cryo-electron tomography,cryo-ET)技术,首次在原位状态下解析了光刻胶分子在液相环境中的微观三维结构、界面分布与缠结行为,指导开发出可显著减少光刻缺陷的产业化方案。相关论文近日刊发于《自然-通讯》。

“显影”是光刻的核心步骤之一,通过显影液溶解光刻胶的曝光区域,将电路图案精确转移到硅片上。光刻胶如同刻画电路的颜料,它在显影液中的运动,直接决定电路画得准不准、好不好,进而影响芯片良率。长期以来,光刻胶在显影液中的微观行为是“黑匣子”,工业界的工艺优化只能靠反复试错,这成为制约7纳米及以下先进制程良率提升的关键瓶颈之一。

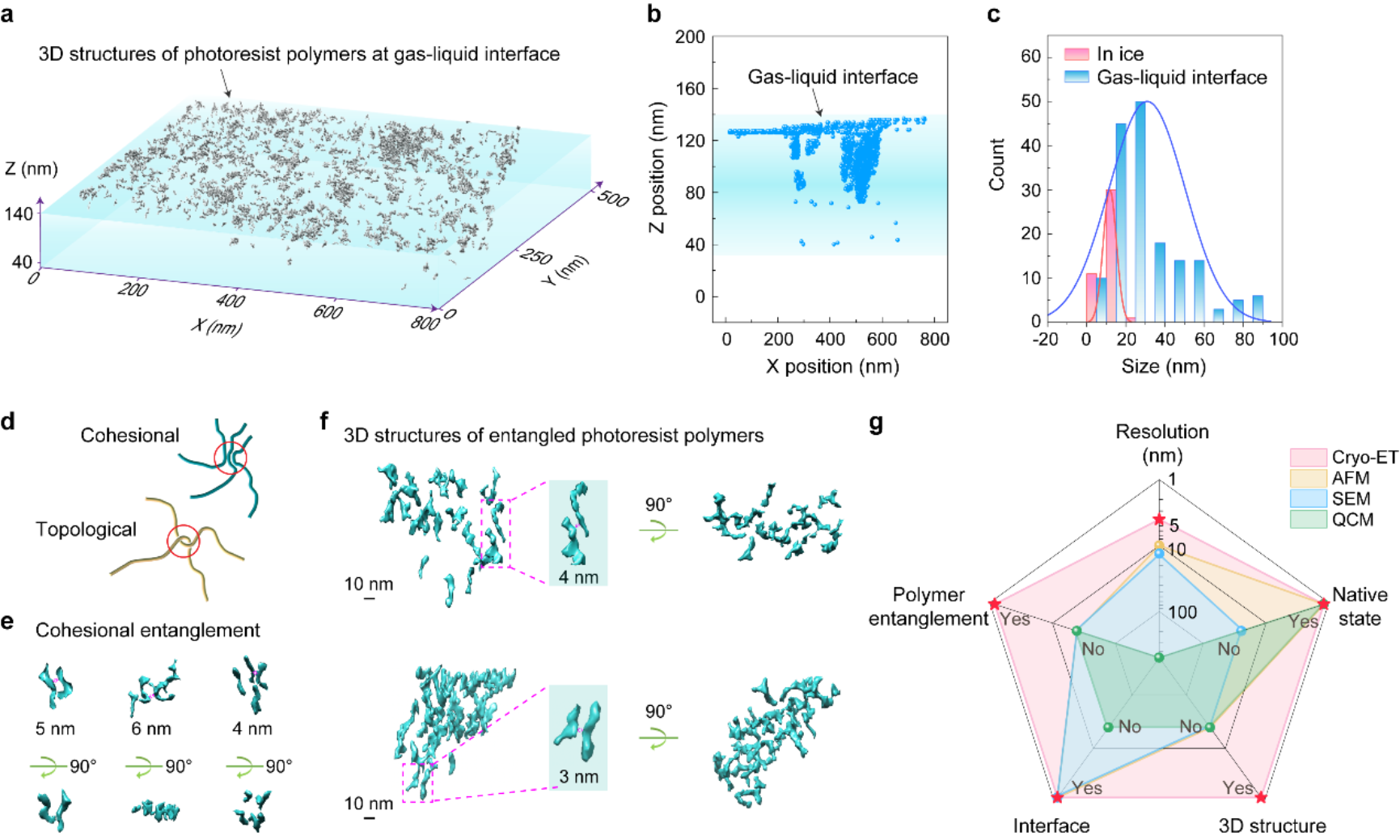

为破解难题,研究团队首次将冷冻电子断层扫描技术引入半导体领域。他们在晶圆上进行标准的光刻曝光后,将含有光刻胶聚合物的显影液快速吸取到电镜载网上,并在毫秒内将其急速冷冻至玻璃态,“定格”光刻胶在溶液中的真实状态。

随后,研究人员在冷冻电镜中倾斜该样品,采集一系列倾斜角度下的二维投影图像,再基于计算机三维重构算法,将这些二维图像融合成一张高分辨率的三维视图,分辨率优于5纳米。这种方法一举解决了传统技术无法原位、三维、高分辨率观测的三大痛点。

该技术带来诸多新发现。论文通讯作者之一、北京大学化学与分子工程学院高毅勤教授介绍,以往业界认为溶解后的光刻胶聚合物主要分散在液体内部,然而三维图像显示它们大多吸附在气液界面;团队还首次直接观察到光刻胶聚合物的“凝聚缠结”,其依靠较弱的力或者疏水相互作用结合;而且,吸附在气液界面的聚合物更易发生缠结,形成平均尺寸约30纳米的团聚颗粒,这些“团聚颗粒”正是潜在的缺陷根源,它们容易沉积到精密的电路图案上,让本该分开的电路连在一起。

团队为控制缠结提出了两项实用方案:适当提高曝光后烘烤温度,抑制聚合物缠结,减少大团聚体生成;优化显影工艺,让晶圆表面始终有连续液膜,使其可以带走聚合物,避免其沉积。两种方案结合,12英寸晶圆表面的光刻胶残留物引起的图案缺陷被成功消除,缺陷数量降幅超过99%。

彭海琳表示,冷冻电子断层扫描技术为在原子/分子尺度上解析各类液相界面反应提供了强大工具。深入掌握液体中聚合物的结构与微观行为,可推动先进制程中光刻、蚀刻和湿法清洗等关键工艺的缺陷控制与良率提升。

网友评论

网友评论